### General Description

The MAX3664 low-power transimpedance preamplifier for 622Mbps SDH/SONET applications consumes only 85mW. Operating from a single +3.3V supply, it converts a small photodiode current to a measurable differential voltage. A DC cancellation circuit provides a true differential output swing over a wide range of input current levels, thus reducing pulse-width distortion. The differential outputs are back-terminated with  $60\Omega$  per side.

The transimpedance gain is nominally  $6k\Omega$ . For input signal levels beyond approximately  $100\mu$ Ap-p, the amplifier will limit the output swing to 900mV. The MAX3664's low 55nA input noise provides a typical sensitivity of -33.2dBm in 1300nm, 622Mbps receivers.

The MAX3664 is designed to be used in conjunction with the MAX3675 clock recovery and data retiming IC with limiting amplifier. Together, they form a complete 3.3V, 622Mbps SDH/SONET receiver.

In die form, the MAX3664 is designed to fit on a header with a PIN diode. It includes a filter connection, which provides positive bias for the photodiode through a 1k $\Omega$  resistor to V<sub>CC</sub>. The device is also available in 8-pin SO and  $\mu$ MAX packages.

### Applications

SDH/SONET Receivers PIN/Preamplifier Receivers

Regenerators for SDH/SONET

#### \_Features

- Single +3.3V Supply Operation

- ✤ 55nA<sub>RMS</sub> Input-Referred Noise

- 6kΩ Gain

- 85mW Power

- ♦ 300µA Peak Input Current

- 200ps Max Pulse-Width Distortion

- + Differential Output Drives 100Ω Load

- 590MHz Bandwidth

#### **Ordering Information**

| PART        | TEMP. RANGE    | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX3664E/D  | -40°C to +85°C | Dice        |

| MAX3664ESA  | -40°C to +85°C | 8 SO        |

| MAX3664EUA* | -40°C to +85°C | 8 μΜΑΧ      |

\* Contact factory for package availability.

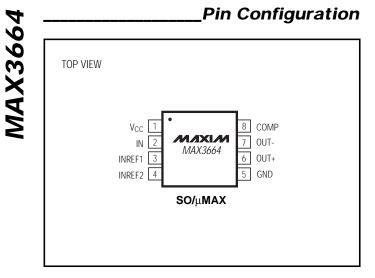

Pin Configuration appears at end of data sheet.

#### V<sub>CC</sub> (+3.3V) 0.01µF V<sub>CC</sub> (+3.3V) 1k $\sim$ (FILT) 100pl 47nF INREF2 + DATA DATA INRFF1 OUT. AND *ก*и л х เ *л* เ LIMITING $100\Omega >$ CLOCK AMP OUT RECOVERY IN CLK COMP 47nF ĠND MAXIM MAX3675 400pF () ARE FOR MAX3664E/D (DICE) ONLY.

###

\_\_\_ Maxim Integrated Products 1

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800. For small orders, phone 408-737-7600 ext. 3468.

### **Typical Application Circuit**

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> 0.5V to +5.5V                         | V |

|-------------------------------------------------------|---|

| Continuous Current                                    |   |

| IN, INREF1, INREF2, COMP, FILT5m/                     | 4 |

| OUT+, OUT25m/                                         | 4 |

| Continuous Power Dissipation ( $T_A = +85^{\circ}C$ ) |   |

| SO (derate 5.88mW/°C above +85°C)                     | V |

| µMAX (derate 4.1mW/°C above +85°C)268mV               | V |

| Operating Junction Temperature (die) | 40°C to +150°C |

|--------------------------------------|----------------|

| Processing Temperature (die)         | +400°C         |

| Storage Temperature Range            |                |

| Lead Temperature (soldering, 10sec)  | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.3V \pm 0.3V, COMP = GND, 100\Omega$  load between OUT+ and OUT-,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Notes 1, 2)

| PARAMETER                    | SYMBOL    | CONDITIONS                              | MIN | TYP                   | MAX  | UNITS |

|------------------------------|-----------|-----------------------------------------|-----|-----------------------|------|-------|

| Input Bias Voltage           | VIN       | I <sub>IN</sub> = 0 to 300µA            |     | 0.8                   | 0.95 | V     |

| Gain Nonlinearity            |           | $I_{IN} = 0$ to $20\mu A$               |     |                       | ±5   | %     |

| Supply Current               | Icc       | $I_{IN} = 0$                            | 12  | 25                    | 35   | mA    |

| Small-Signal Transimpedance  | Z21       | Differential output                     | 4.5 | 6                     | 7.5  | kΩ    |

| Output Common-Mode Level     |           |                                         |     | V <sub>CC</sub> - 1.3 |      | V     |

| Power-Supply Rejection Ratio | PSRR      | f < 1MHz, referred to output            | 20  |                       |      | dB    |

| Differential Output Offset   | Δνουτ     | $I_{IN} = 200 \mu A, C_{COMP} = 400 pF$ |     | ±7                    |      | mV    |

| Output Impedance (per side)  | Zout      |                                         | 40  | 60                    | 75   | Ω     |

| Maximum Output Voltage       | Vout(max) | I <sub>IN</sub> = 300µA                 |     |                       | 950  | mV    |

| Filter Resistor (die only)   | RFILT     |                                         | 800 | 1000                  | 1200 | Ω     |

**Note 1:** Dice are tested at  $T_i = +27^{\circ}C$ .

**Note 2:**  $\mu$ MAX package tested at T<sub>A</sub> = +25°C to +85°C.

### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.3V \pm 0.3V, C_{COMP} = 400pF, C_{IN} = 1.1pF$ , outputs terminated into 50 $\Omega$ , 8-pin SO package in MAX3664 EV board, T<sub>A</sub> = +25°C, unless otherwise noted.) (Notes 3, 4)

| PARAMETER                          | SYMBOL | CONDITIONS                                                        | MIN | TYP | MAX | UNITS |

|------------------------------------|--------|-------------------------------------------------------------------|-----|-----|-----|-------|

| Small-Signal Bandwidth             | BW-3dB | Relative to gain at 10MHz                                         |     | 590 |     | MHz   |

| Low-Frequency Cutoff               |        |                                                                   |     |     | 150 | kHz   |

| Pulse-Width Distortion<br>(Note 5) | PWD    | 2µA to 100µA peak input current,<br>50% duty cycle, 1–0 pattern   |     | 6   | 100 | - ps  |

|                                    |        | 100µA to 300µA peak input current,<br>50% duty cycle, 1–0 pattern |     | 80  | 200 |       |

| RMS Noise Referred to Input        | in     | $C_{IN} = 0.3 pF$ (Note 6), $I_{IN} = 0$                          |     | 55  |     | - nA  |

|                                    |        | C <sub>IN</sub> = 1.1pF (Note 6), I <sub>IN</sub> = 0             |     | 73  | 86  |       |

Note 3: AC Characteristics are guaranteed by design.

Note 4: C<sub>IN</sub> is the total capacitance at IN.

**Note 5:** PWD =  $\left| \frac{2 \times \text{Pulse width - Period}}{2} \right|$

Note 6: DC to 470MHz, measured with 3-pole Bessel filter at output.

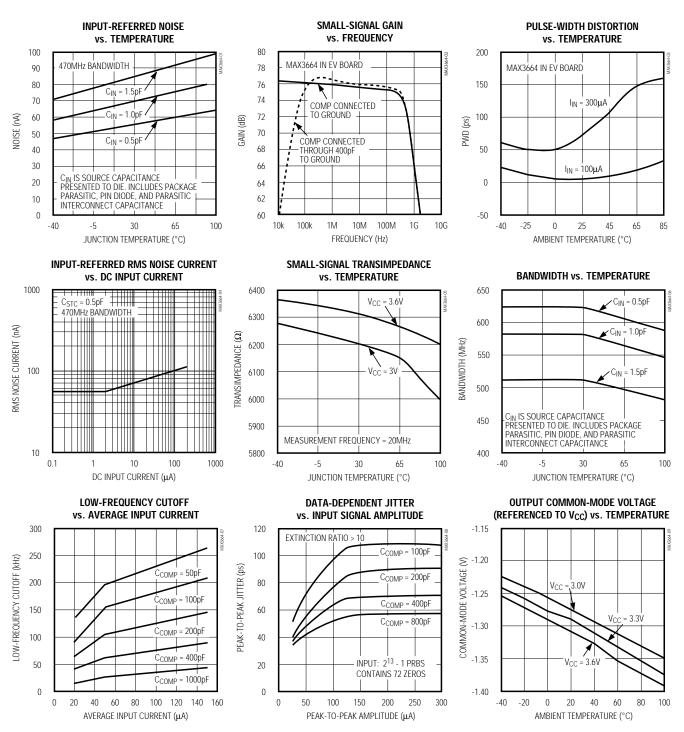

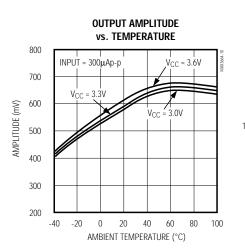

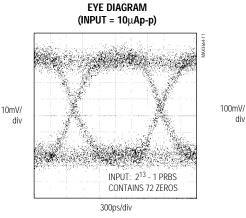

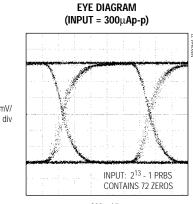

**Typical Operating Characteristics**

(V<sub>CC</sub> = +3.3V, C<sub>COMP</sub> = 400pF, T<sub>A</sub> =  $+25^{\circ}$ C, unless otherwise noted.)

**MAX3664**

### \_Typical Operating Characteristics (continued)

(V<sub>CC</sub> = +3.3V, C<sub>COMP</sub> = 400pF, T<sub>A</sub> =  $+25^{\circ}$ C, unless otherwise noted.)

300ps/div

| PIN  | NAME                                                                                                                                                                                                          | FUNCTION                                                                                                                                                                            |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1    | Vcc                                                                                                                                                                                                           |                                                                                                                                                                                     |  |

| 1    | VCC                                                                                                                                                                                                           | +3.3V Supply Voltage                                                                                                                                                                |  |

| 2    | IN                                                                                                                                                                                                            | Signal Input                                                                                                                                                                        |  |

| 3, 4 | INREF1,<br>INREF2                                                                                                                                                                                             | Input References 1 and 2. Connect to photodetector AC ground.                                                                                                                       |  |

| 5    | GND                                                                                                                                                                                                           | Ground                                                                                                                                                                              |  |

| 6    | OUT+                                                                                                                                                                                                          | Noninverting Voltage Output. Current flowing into IN causes V <sub>OUT+</sub> to increase.                                                                                          |  |

| 7    | OUT-                                                                                                                                                                                                          | Inverting Voltage Output. Current flow-<br>ing into IN causes V <sub>OUT</sub> . to decrease.                                                                                       |  |

| 8    | COMP External Compensation Capacitor for<br>DC cancellation loop. Connect 400pF<br>or more from COMP to GND for nor-<br>mal operation. Connect COMP directl<br>to GND to disable the DC cancellation<br>loop. |                                                                                                                                                                                     |  |

| _    | FILT*                                                                                                                                                                                                         | FILT* Filter Connection. Provides positive bias for photodiode through a $1k\Omega$ resistor to $V_{CC}$ . See Step 3: Designing Filters. (This pad is accessible on the die only.) |  |

### Pin Description

\* MAX3664E/D (die) only.

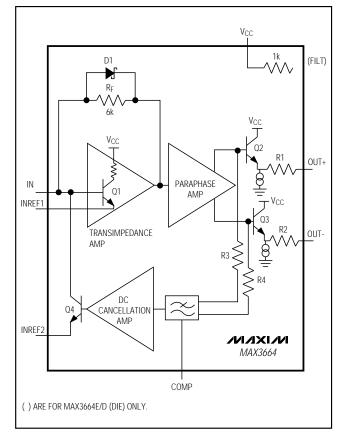

Figure 1. Functional Diagram

M/IXI/M

### Detailed Description

The MAX3664 is a transimpedance amplifier designed for 622Mbps SDH/SONET applications. It comprises a transimpedance amplifier, a paraphase amplifier with emitter-follower outputs, and a DC cancellation loop. Figure 1 is a functional diagram of the MAX3664.

#### Transimpedance Amplifier

The signal current at IN flows into the summing node of a high-gain amplifier. Shunt feedback through RF converts this current to a voltage with a gain of  $6k\Omega$ . Diode D1 clamps the output voltage for large input currents. INREF1 is a direct connection to the emitter of the input transistor, and must be connected directly to the photodetector AC ground return for best performance.

#### Paraphase Amplifier

The paraphase amplifier converts single-ended inputs to differential outputs, and introduces a voltage gain of 2. This signal drives a pair of internally biased emitter followers, Q2 and Q3, which form the output stage. Resistors R1 and R2 provide back-termination at the output, absorbing reflections between the MAX3664 and its load.

The output emitter followers are designed to drive a 100 $\Omega$  differential load between OUT+ and OUT-. They can also drive higher output impedances, resulting in increased gain and output voltage swing.

#### **DC Cancellation Loop**

The DC cancellation loop removes the DC component of the input signal by using low-frequency feedback. This feature centers the signal within the MAX3664's dynamic range, reducing pulse-width distortion on large input signals.

The output of the paraphase amplifier is sensed through resistors R3 and R4 and then filtered, amplified, and fed back to the base of transistor Q4. The transistor draws the DC component of the input signal away from the transimpedance amplifier's summing node.

The COMP pin sets the DC cancellation loop's response. Connect 400pF or more between COMP and GND for normal operation. Connect the pin directly to GND to disable the loop. The DC cancellation loop can sink up to 300µA of current at the input. When operated with  $C_{COMP} = 400 pF$ , the loop takes approximately 20µs to stabilize.

The MAX3664 minimizes pulse-width distortion for data sequences that exhibit a 50% duty cycle. A duty cycle other than 50% causes the device to generate pulsewidth distortion.

DC cancellation current is drawn from the input and adds noise. For low-level signals with little or no DC

component, this is not a problem. Preamplifier noise will increase for signals with significant DC component.

### \_Applications Information

The MAX3664 is a low-noise, wide-bandwidth transimpedance amplifier that is ideal for 622Mbps SDH/ SONET receivers. Its features allow easy design into a fiber optic module, in four simple steps.

#### Step 1: Selecting a Preamplifier for a 622Mbps Receiver

Fiber optic systems place requirements on the bandwidth, gain, and noise of the transimpedance preamplifier. The MAX3664 optimizes these characteristics for SDH/SONET receiver applications that operate at 622Mbps.

In general, the bandwidth of a fiber optic preamplifier should be 0.6 to 1 times the data rate. Therefore, in a 622Mbps system, the bandwidth should be between 375MHz and 622MHz. Lower bandwidth causes pattern-dependent jitter and a lower signal-to-noise ratio, while higher bandwidth increases thermal noise. The MAX3664 typical bandwidth is 590MHz, making it ideal for 622Mbps applications.

The preamplifier's transimpedance must be high enough to ensure that expected input signals generate output levels exceeding the sensitivity of the limiting amplifier (quantizer) in the following stage. The MAX3675 clock recovery and limiting amplifier IC has an input sensitivity of 3.6mVp-p, which means that 3.6mVp-p is the minimum signal amplitude required to produce a fully limited output. Therefore, when used with the MAX3664, which has a  $6k\Omega$  transimpedance, the minimum detectable photodetector current is 600nA.

It is common to relate peak-to-peak input signals to average optical power. The relationship between optical input power and output current for a photodetector is called the responsivity ( $\rho$ ), with units Amperes/Watt (A/W). The photodetector peak-to-peak current is related to the peak-to-peak optical power as follows:

#### Ip-p = (Pp-p)(p)

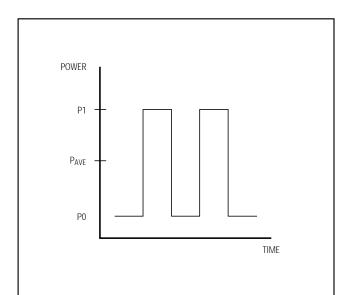

Based on the assumption that SDH/SONET signals maintain a 50% duty cycle, the following equations relate peak-to-peak optical power to average optical power and extinction ratio (Figure 2):

Average Optical Power = PAVE = (P0 + P1) / 2

Extinction Ratio =  $r_e = P1 / P0$

Peak-to-Peak Signal Amplitude = Pp-p = P1 - P0 Therefore,

$P_{AVF} = P_{P-p} (1 / 2)[(r_{e} + 1) / (r_{e} - 1)]$

In a system where the photodiode responsivity is 0.9A/W and the extinction ratio is 10, the MAX3664/ MAX3675 receiver with 670nA gain sensitivity will deliver a fully limited output for signals of average optical power larger than:

$(600nA / 0.9A/W)(1 / 2)(11 / 9) = 407nW \implies -33.9dBm$

Sensitivity is a key specification of the receiver module. The ITU/Bellcore specifications for SDH/SONET receivers require a link sensitivity of -27dBm with a bit error rate (BER) of 1E - 10. There is an additional 1dB power penalty to accommodate various system losses; therefore, the sensitivity of a 622Mbps receiver must be better than -28dBm.

Although several parameters affect sensitivity (such as the quantizer sensitivity and preamplifier gain, as previously discussed), most fiber optic receivers are designed so that noise is the dominant factor. Noise from the high-gain transimpedance amplifier, in particular, determines the sensitivity. The noise generated by the MAX3664 can be modeled with a Gaussian distribution. In this case, a BER of 1E - 10 corresponds to a peak-to-peak signal amplitude to RMS noise ratio (SNR) of 12.7. The MAX3664's typical input-referred noise, i<sub>n</sub>, (bandwidth-limited to 470MHz) is 55nA<sub>RMS</sub>. Therefore, the minimum input for a BER of 1E - 10 is (12.7 x 55nA) = 700nAp-p. Rearranging the previous equations in these terms results in the following relation:

Optical Sensitivity (dBm) = -10log[( $i_n / \rho$ )(SNR)(1/2)( $r_e + 1$ ) / ( $r_e - 1$ )(1000)]

Figure 2. Optical Power Definitions

At room temperature, with  $r_e$  = 10, SNR = 12.7,  $i_n$  = 55nA, and  $\rho$  = 0.9A/W, the MAX3664 sensitivity is -33.2dBm. At +85°C, noise increases to 62nA and sensitivity decreases to -32.7dBm. The MAX3664 provides 4.7dB margin over the SDH/SONET specifications, even at +85°C.

The largest allowable input to an optical receiver is called the input overload. The MAX3664's largest input current (I<sub>max</sub>) is 300µAp-p, with 200ps of pulse-width distortion. The pulse-width distortion and input current are closely related (see *Typical Operating Characteristics*). If the clock recovery circuit can accept more pulse-width distortion, a higher input current might be acceptable. For worst-case responsivity and extinction ratio,  $\rho = 1A/W$  and  $r_e = \infty$ , the input overload is:

Overload (dBm) =  $-10\log (I_{max})(1 / 2)(1000)$

For  $I_{max} = 300\mu A$ , the MAX3664 overload is -8.2dBm.

#### **Step 2: Selecting Time Constants**

A receiver built with the MAX3664 will have a bandpass frequency response. The low-frequency cutoff causes unwanted data-dependent jitter and sensitivity loss. Because SDH/SONET data streams contain scrambled data, certain data sequences may generate continuous successions of 1s or 0s. The low-frequency cutoff forces the output of such sequences to zero, ultimately causing a sensitivity reduction. The SDH specifications state that a receiver must be able to handle up to 72 consecutive bits of the same value within the data. Therefore, choose the low-frequency cutoff to ensure an acceptable amount of data-dependent jitter and sensitivity loss.

Determine the reduction in signal-to-noise ratio due to a transitionless sequence of duration t as follows:

$$SNR_{IOSS} = 1 - e^{-t} / \tau = 1 - e^{-(2\pi f_{C}t)}$$

where  $\tau$  is the time constant of the offset correction, f<sub>c</sub> is the low-frequency cutoff, and t is the time for 72 bits (116ns for a 622Mbps data rate).

Suppose that the receiver should not have more than 0.25dB (6%) of sensitivity loss due to a 72-bit transition-less sequence. This means that:

$(1 - e - (2\pi f_c)(116ns)) < 0.06$

$f_{\rm C} = (\ln 0.94) / [(-2\pi)(116 \text{ns})] = 85 \text{kHz} (\text{max})$

The loss of sensitivity is a concern only when the SNR is small (close to 12.7), which occurs with input currents less than  $3\mu$ Ap-p.

The cutoff frequency also affects the data-dependent jitter (DDJ). DDJ due to low-frequency cutoff can be approximated as droop / slope, where the slope in V/sec is measured at the 50% crossing of an eye diagram, and droop is the loss-of-signal to noise calculated above as  $1 - e(2\pi fct)$ . The slope at the 50% crossing is typically two times the 10% to 90% slope, which is approximately 0.35 / bandwidth. For a 622Mbps receiver with a 470MHz bandwidth, the 10% to 90% rise time is approximately 750ps. The slope through the 50% crossing will be approximately:

Amplitude (2)(0.8) / 750ps = 1.6 Amplitude / 750ps = 2E9 Amplitude V/sec

$DDJ = 2 [Amplitude (1 - e-(2\pi f_{c}t))] / [2.0E9 Amplitude] = (1 - e-(2\pi f_{c}t)) / (1E9) OR$

$f_{C} = -ln[1 - (1.0E9)(DDJ)] / [2\pi t]$

If the maximum allowable DDJ is 100ps, and t = 112ns for a 72-bit sequence, then the maximum low-frequency cutoff is 150kHz.

Several circuits in the receiver can determine the lowfrequency cutoff. In a receiver using the MAX3664 and MAX3675, there are three locations for concern:

- 1) The MAX3664's DC cancellation circuit.

- 2) The coupling capacitors between the MAX3664 outputs and MAX3675 inputs.

- 3) The MAX3675's offset correction circuit.

The highest cutoff frequency in the system determines the amount of data-dependent jitter created.

The time constants of the MAX3675's offset correction and of the coupling capacitors should be separated by a factor of ten (one decade) to prevent low-frequency oscillations.

For example, select the offset correction of the MAX3664 to set the receiver cutoff frequency. Note that the MAX3664's low-frequency cutoff increases with average input current. Since DDJ increases with  $f_c$ , it follows that DDJ increases as average input increases. When the input signal is large enough to limit the outputs, however, DDJ does not increase. Therefore, the maximum DDJ results from the lowest input that causes the MAX3664 to have limited outputs (see *Typical Operating Characteristics*), which is about 150µAp-p. When selecting a capacitor for the COMP pin that achieves your desired DDJ, use the data from *Typical Operating Characteristics* at I<sub>INPUT</sub> = 150µA.

In summary, use the following method to select the lowfrequency cutoff that will provide the sensitivity and DDJ required for SDH/SONET receivers:

- 1) Determine the longest time without transitions.

- 2) Determine the acceptable loss of SNR ratio, and the acceptable DDJ due to the transitionless time.

- 3) Estimate the low-frequency cutoff required for either the worst-case SNR loss or for DDJ.

- Select the location in the receiver to determine the highest cutoff frequency. Normally, the MAX3664 would determine the dominant low-frequency cutoff. Then select all other low-frequency cutoffs one decade lower.

- 5) Select a capacitor for the COMP pin from the *Typical Operating Characteristics* graphs. 400pF is adequate for most 622Mbps SDH/SONET applications.

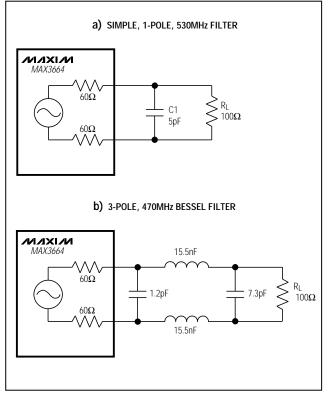

#### Step 3: Designing Filters

The MAX3664's noise performance is a strong function of the circuit's bandwidth, which changes over temperature and varies from lot to lot. The receiver sensitivity can be improved by adding filters to limit this bandwidth. Filter designs can range from a one-pole filter using a single capacitor, to more complex filters using inductors. Figure 3 illustrates two examples: the simple filter provides moderate roll-off with minimal components, while the complex filter provides a sharper rolloff and better transient response.

Supply voltage noise at the cathode of the photodiode produces a current I = C<sub>PHOTO</sub> ( $\Delta V/\Delta t$ ), which reduces the receiver sensitivity. C<sub>PHOTO</sub> is the photodiode capacitance.

The FILT resistor of the MAX3664, combined with an external capacitor (see *Typical Operating Circuit*) can be used to reduce this noise. The external capacitor (C<sub>FILT</sub>) is placed in parallel with the photodiode. Current generated by supply noise is divided between C<sub>FILT</sub> and C<sub>PHOTO</sub>. The input noise current due to supply noise is (assuming the filter capacitor is much larger than the photodiode capacitance):

$$I_{\text{NOISE}} = \frac{(V_{\text{NOISE}})(C_{\text{PHOTO}})}{(R_{\text{FILT}})(C_{\text{FILTER}})}$$

If the amount of tolerable noise is known, then the filter capacitor can be easily selected:

$$C_{FILT} = \frac{(V_{NOISE})(C_{PHOTO})}{(R_{FILT})(I_{NOISE})}$$

For example, with maximum noise voltage = 100mVp-p, CPHOTO = 0.5pF, RFILT = 1k $\Omega$ , and INOISE selected to be 5nA (1/10 of MAX3664 input-referred noise):

$$C_{FILT} = (0.1)(0.5E - 12)/[(1000)(5E - 9)] = 10nF$$

#### Step 4: Designing a Low-Capacitance Input

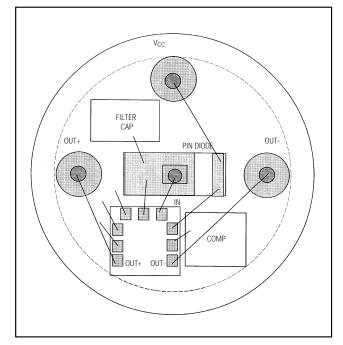

Noise performance and bandwidth are adversely affected by stray capacitance on the input node. Select a low-capacitance photodiode and use good high-frequency design and layout techniques to minimize capacitance on this pin. The MAX3664 is optimized for 0.5pF of capacitance on the input approximately the capacitance of a photodetector diode sharing a common header with the MAX3664 in die form.

Figure 3. Filter Design Examples

Photodiode capacitance changes significantly with bias voltage. With a 3.3V supply voltage, the reverse voltage on the PIN diode is only 2.5V. If a higher voltage supply is available, apply it to the diode to significantly reduce capacitance.

Take great care to reduce input capacitance. With the SO and  $\mu$ MAX versions of the MAX3664, the package capacitance is about 0.3pF, and the PC board between the MAX3664 input and the photodiode can add parasitic capacitance. Keep the input line short, and remove power and ground planes beneath it. Packaging the MAX3664 into a header with the photodiode provides the best possible performance. It reduces parasitic capacitance to a minimum, resulting in the lowest noise and the best bandwidth.

///XI//

#### INREF1 and INREF2

Connect INREF1 and INREF2 as close to the AC ground of the photodetector diode as possible. The photodetector AC ground is usually the ground of the filter capacitor from the photodetector anode. The total loop (from INREF1/INREF2, through the bypass capacitor and the diode, and back to IN) should be no more than 2 cm. long.

#### Wire Bonding

For high current density and reliable operation, the MAX3664 uses gold metallization. Make connections to the die with gold wire only, and use ball bonding techniques (wedge bonding is not recommended). Die-pad size is 4 mils square, with a 6 mil pitch. Die thickness is 12 mils.

#### Vcc and Ground

Use good high-frequency design and layout techniques. The use of a multilayer circuit board with separate ground and  $V_{CC}$  planes is recommended. Take care to bypass  $V_{CC}$  and to connect the GND pin to the ground plane with the shortest possible traces.

Figure 4. Suggested Layout for TO-46 Header

M/X/M

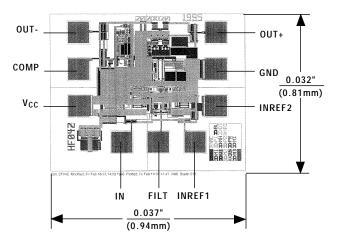

### \_Chip Topography

TRANSISTOR COUNT: 73 SUBSTRATE CONNECTED TO GND

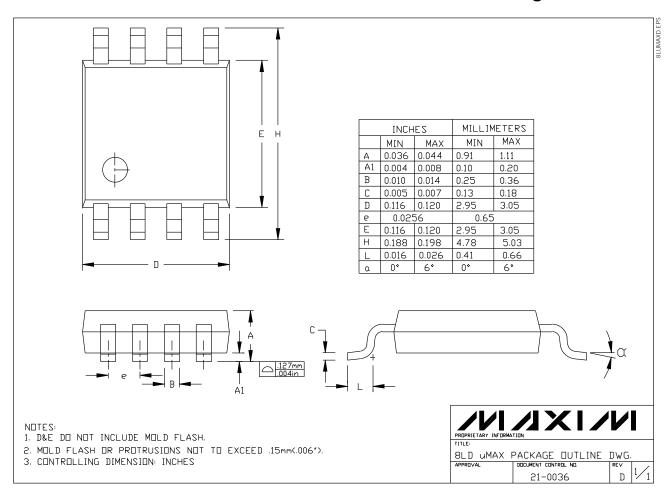

### Package Information

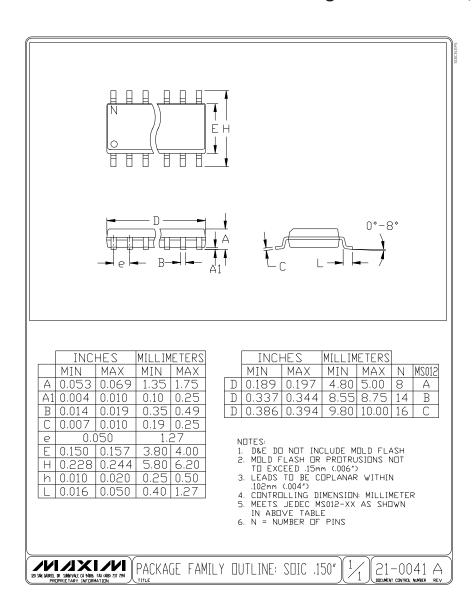

Package Information (continued)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 1997 Maxim Integrated Products Printed USA MAXIM is a registered trademark of Maxim Integrated Products.

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated: MAX3664ESA-T